16+ verilog vector

First the Verilog code for 1-bit full adder is written. Vectors are used to represent multi-bit busses.

Fixed Point Matrix Multiplication In Verilog Full Code Tutorials Fpga4student Com

000_1 001_0 010_0 011_0 100_1 101_1 110_0 111_0 file expected outputs.

. We use relational operators to compare the value of two different variables in SystemVerilog. But in hardware many ports can have more than one bit has an input. Its the same as 16b0 or 16d0 in this case 16 bit vector with all bits 0.

8-bit reg vector with. While writing the Verilog code for 16-bit Ripple carry adder the same procedure is used. H ff is 00ff hex default 16 bit 16h ff is.

Assign out70 in07. Examplev contains vectors of abc_yexpected. Verilog is a HARDWARE DESCRIPTION LANGUAGE HDL which is used to describe a digital system such as a network switch or a microprocessor or a memory a flip-flop.

This allows us to declare a signal which has more than one bit. The code snippet below shows the general syntax which. After completing the design for the MIPS processor it is easy to write Verilog code for the MIPS processor.

The h comes into effect e. Logic c handles 0-4095 inclusive 2 12 is 4096. Copy path Copy permalink.

This commit does not belong to any branch on this repository and may belong. From this we can get the 4-bit ripple. Go to line L.

Wire a handles 0-63 inclusive 2 6 is 64. The reg variable data type may have a modifier signed and may have may bits by using the vector modifier msb. You are creating a 32-bit bus result.

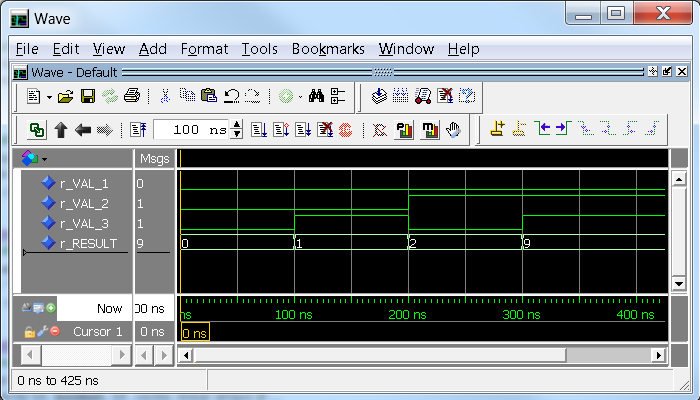

Verilog Testbench Example Test Vector. With 16h0fff which is equivalent to 16d4095. The curly braces mean concatenation from most significant bit MSB on the left down to the least significant bit LSB on the right.

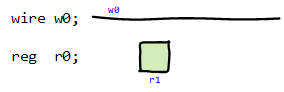

In Verilog we have seen that we have 1-bit data types. Verilog provides the concept of Vectors. Verilog Types and Constants.

A vector to represent a multi bit bus is declared as follows. Does not work because Verilog does not allow vector bit ordering to be flipped. The concatenation operator may save a bit of coding allowing for 1 assign statement.

Verilog-Practice 1_Verilog language 16_Vector3v Go to file Go to file T. In verilog we can use vector types to create data buses. The result of this comparison returns either a.

Register b handles 0-255 inclusive 2 8 is 256. I hope you can proceed. SystemVerilog Relational Operators.

Data-path and control unit of the 16-bit MIPS processor. A b and c are vectors.

Fixed Point Numbers In Verilog Project F Fpga Dev

Verilog Vs Vhdl Learn The Key Differences Of Verilog And Vhdl

![]()

How To Write A Function In Verilog Which Takes A Vector As Input And Outputs A Vector Forum For Electronics

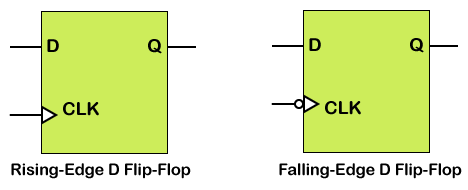

Verilog D Flip Flop Javatpoint

Verilog Case Statement Example

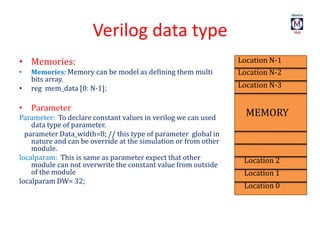

Verilog Hdl

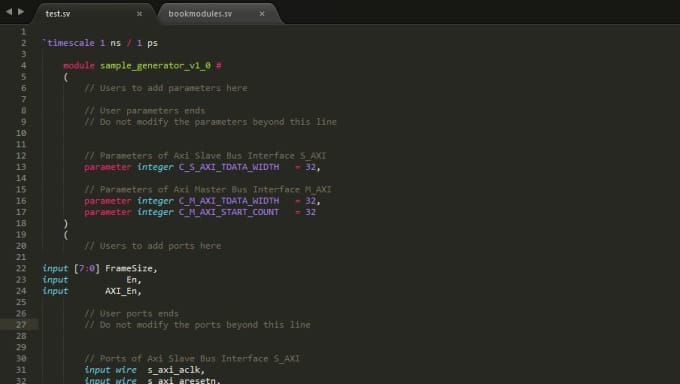

Write Verilog Or System Verilog Code For You And Debug By Casper170 Fiverr

Case Statement Nandland

Antmicro An Open Source Systemverilog Test Suite

Automatic Elaboration And Translation Of Verilog Module The Verilog Download Scientific Diagram

Deal With The Complexity Of Vhdl Verilog And Systemverilog Sigasi

Air Supply Lab Lesson 04 Verilog Scalar Vector And Array

Lecture 16 Signed Integers And Integer Arithmetic

Cse370 Laboratory Tutorial 2

Getting Started With The Verilog Hardware Description Language Technical Articles

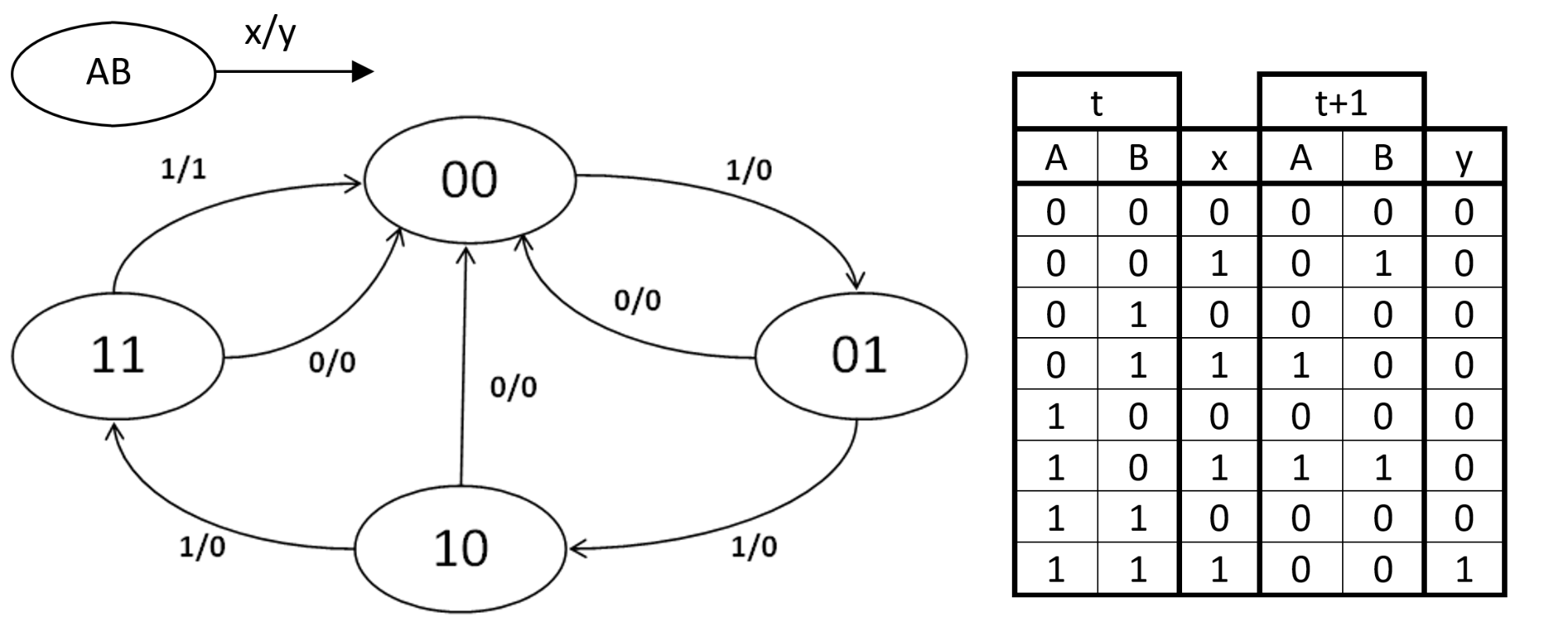

Creating Finite State Machines In Verilog Technical Articles

Modelsim Is Default Value Required For A Verilog Parameter Declaration Stack Overflow